新思科技(Synopsys)強攻先進製程。晶圓廠擴大布局1x奈米先進製程,連帶刺激晶片商積極投入先進製程晶片開發,因而面臨更為艱鉅的設計挑戰;有鑑於此,新思科技推出高效率的設計平台–IC Compiler II,緊扣晶片設計商的需求,期能在每一個先進製程節點都搶占先機。

|

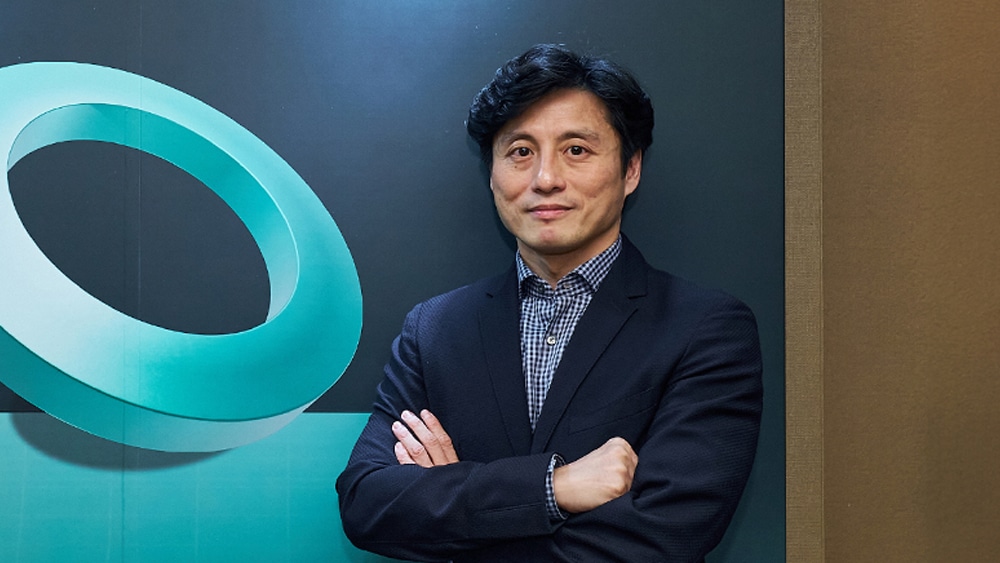

| 新思科技設計事業群資深副總裁羅升俊指出,先進製程需求將加劇晶片的驗證挑戰,因此新的驗證/設計方法須緊貼客戶需求。 |

新思科技設計事業群資深副總裁羅升俊指出,雖然至今22奈米以下的晶片投片試產(Tape-out)數量並不多,不過根據統計,目前市場上在22奈米以下的晶片設計案已超過兩百五十個,且其中有一百一十個以上係位於16/14奈米製程節點,顯見晶片商對於先進製程的需求正在發酵。

羅升俊進一步強調,為了在先進製程市場持續占有一席之地,新思科技一直以來都積極與台積電、三星(Samsung)、英特爾(Intel)、格羅方德(GLOBALFOUNDRIES)等晶圓廠維持密切的合作關係;另一方面,新思科技洞見晶片商在先進製程設計過程中,將面臨更為嚴峻的設計挑戰,因此該公司亦積極改良晶片設計平台,期能搭起晶片商與晶圓廠之間的完美橋梁。

羅升俊表示,新思科技曾做過一項調查,請研發工程師指出從晶片設計到上市的流程中,碰到的前三大挑戰分別為何。調查結果顯示,在預定的時間內完成投片(Tapeout on Schedule)、時序收斂(Timing Closure)不如預期、達成最佳的晶片時序和尺寸(Meeting Timing and Area Goals)三者,是讓工程師最為困擾的前三大難題。

為克服這些挑戰,新思科技的IC Compiler II徹底地奠基在全新的多執行緒(Multi-threaded)架構上,並具備超高容量(Ultra-high-capacity)設計規畫、時脈建造(Clock-building)技術和先進的整體分析收斂(Global-analytical Closure)技術,讓晶片實體設計生產力(Physical Design Throughput)提高十倍。

據了解,IC Compiler II的設計聚焦在全晶片層級(Full Chip-level)上,其背後的支援技術包括新的整體分析優化引擎(Global-analytical Optimization Engine)、全新的時脈產生器(Clock Generator)以及獨特的繞線後(Post-route)優化演算能力,結合這幾項技術可提升面積、時序和功耗的結果品質(QoR)。

羅升俊總結,IC Compiler II能提供十倍速度的設計規畫、五倍速度的設計實作時間(Runtime),同時將記憶體的耗用降低二分之一。如此一來,設計人員能快速評估許多晶片設計平面規畫(Floor-planning)的選項,以便在正確時機著手進行實作。他亦透露,該平台甫推出,即已成功協助Panasonic、艾薩(LSI)、意法半導體(ST)及Imagination等廠商成功完成投片。