看好整合扇出型封裝(Integrated fan-out,InFO)技術未來發展,明導國際(Mentor Graphics)宣布推出一款結合設計、版圖布局和驗證的解決方案,為InFO晶圓級封裝技術的設計應用提供支援。該解決方案包含Calibre nmDRC物理驗證產品、Calibre RVE結果查看平台,以及Xpedition Package Integrator流程。上述解決方案可使InFO技術獨特的扇出層級結構和互聯運用於如行動、消費類等對成本敏感的產品中。

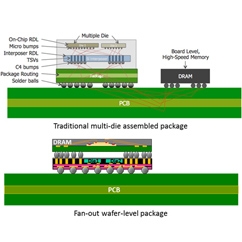

Mentor Graphics市場發展經理兼系統設計師Jamie Metcalfe表示,過往客戶多採用多晶片模組(Multi-Chip Module, MCM)、系統單晶片(SoC)等封裝技術。然而,由於InFO封裝的好處在於可減少更多功率損耗、提升性能、提供更多針腳(Footprint),以及降低更多成本,因此越來越多IC封裝廠採用此一技術。不過,使用InFO封裝技術須先克服三大挑戰,分別為多重元件連結(Multiple Component Connectivity)、不規則形狀(Non-Manhattan Shapes)及不同檔案標準(Disparate File Standards)。為此,明導推出新解決方案,以解決上述問題。

新推出的解決方案允許IC和封裝設計工程師直接透過整合於Xpedition Package Integrator流程中Calibre nmDRC工具查看和交互追蹤結果,以驗證InFO互聯結構。由於此流程是藉由已經驗證整合的Calibre RVE工具,其具有自動化Sign-off功能,能更輕易地改正Calibre nmDRC產品顯示的任何問題,並簡化未來特性和功能的增加過程。

IC設計工程師已廣泛採用Calibre nmDRC工具作為多代製程(Multiple-process) Sign-off解決方案。通過與Xpedition Package Integrator整合,如今他們可以在執行協同驗證時與封裝開發人員看到相同的視圖。

新款解決方案目前已可支援台積電(TSMC)之InFO封裝技術,Mentor Graphics Designn to Silicon事業部副總裁兼總經理Joe Sawicki指出,將Calibre nmDRC技術與Xpedition Package Integrator流程相整合式該公司支援TSMC InFO技術走出堅實第一步。明導將繼續與TSMC及其他生態系統合作,藉由建立更多功能的產品發展藍圖,在現有的基礎上擴大合作,使TSMC InFO的產品用戶可以進一步加速產品上市時間。