Mentor近期宣布,該公司的多項IC設計工具已獲得台積電的N5和N6製程技術認證。此外,Mentor與台積電的合作關係已擴展到先進封裝技術,可進一步利用Mentor Calibre平台的3DSTACK封裝技術來支援台積電的先進封裝平台。

台積電的N5和N6製程技術可協助許多全球領先的IC設計公司提高處理器效能、縮小尺寸並降低功耗,以應對汽車、物聯網、高效能運算、5G行動/基礎設施、人工智慧等領域激烈的市場競爭。

Mentor的IC部門執行副總裁Joe Sawicki表示,Mentor與台積電長期合作並且擁有豐碩的成果,如此緊密的夥伴關係將持續協助共同客戶開發出高度創新和差異化的IC。很高興Mentor設計平台能夠獲得台積電最新的半導體製程技術認證,雙方的夥伴關係得到了更進一步擴展。

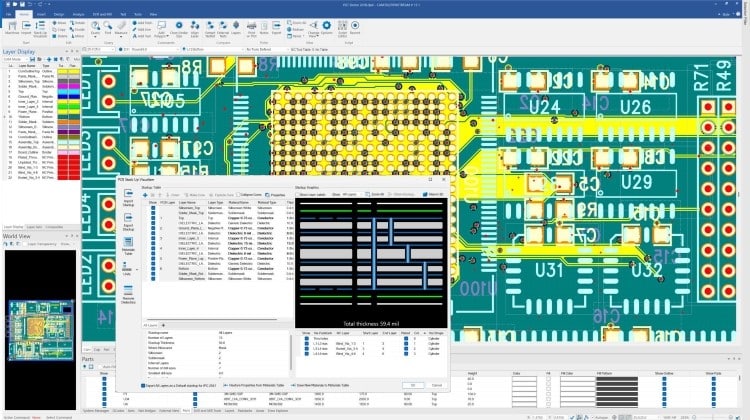

最近通過台積電N5和N6製程認證的Mentor IC設計技術包括Calibre nmPlatform,它是IC實體驗證領域的工具。Calibre可為全球成功的晶片製造商和IC設計人員提供出色的效能、準確度和可靠性驗證方案;Calibre xACT抽取工具─Calibre nmPlatform中的組成元件,可提供強大的寄生參數抽取功能和高準確度的數據,以供布局後分析和模擬之用;Mentor的Analog FastSPICE(AFS)平台─可為奈米類比、射頻(RF)、混合訊號、記憶體和客制化數位電路提供先進的電路驗證。

除了獲得這些認證,Mentor亦宣布,其AFS平台現在可支援台積電的行動裝置和高效能運算(HPC)設計平台。此認證可協助為HPC應用提供類比、混合訊號和射頻(RF)設計的Mentor客戶,使用台積電的最新製程技術充滿信心地進行晶片驗證。Mentor還同時宣布將與台積電合作,進一步利用Calibre的3DSTACK封裝工具來支援台積電的CoWoS封裝技術。該技術採用矽中介層作為晶粒間端口連接檢查的解決方案,Calibre xACT可用來提供寄生參數抽取。

台積電設計建構行銷事業處資深處長Suk Lee表示,作爲台積電重要的合作夥伴,Mentor持續提供豐富多樣的設計工具和平台,以支援台積電最先進的製程技術。期待與Mentor繼續共同努力,透過電子設計自動化 (EDA) 工具協助雙方的共同客戶運用5奈米製程這樣的TSMC領先技術提升晶片功率和效能,運用先進的EDA工具成功實現晶片設計。