2025年將是PCIe介面正式跨入6.0世代的關鍵年。為確保採用PCIe 6.0的處理器平台在推出的第一時間,就有相容性無虞的周邊配套,PCI-SIG早在2024年就已經展開初步相容性測試(Preliminary FYI Testing),並預計在2025年發表首批整合商名單。晶片廠、伺服器整機與板卡廠為了擠進第一波取得認證的供應商清單,無不卯足全力。儀器業者安立知(Anritsu)亦利用PCI-SIG開發者大會台北場及相容性工作坊(Workshop)的機會,協助開發者進行設計驗證,以確保產品能順利通過PCIe 6.0相容性測試。

安立知技術經理王榆淙表示,PCI-SIG是一個對相容性驗證要求相當嚴謹的產業標準組織,每年都會巡迴世界各地舉辦多場相容性測試活動,讓PCIe生態系裡的成員能帶著自家的待測物(DUT)到工作坊裡與其他業者的產品進行實地測試,以便讓PCIe的開發者能對自家產品的相容性有更好的掌握度。但隨著PCIe介面的頻寬提升,訊號完整性的挑戰變得更加艱鉅,現在若只靠PCI-SIG舉辦的活動來進行插拔測試,肯定是不夠的。因此,近年來PCIe的測試越來越倚重儀器模擬,儀器供應商會根據PCI-SIG提供的測試條件跟規範,發展出對應的Tx、Rx、線纜等測試解決方案,而不是完全仰賴實物測試。

王榆淙透露,隨著PCIe 6.0時代的腳步越來越近,客戶將面臨更緊迫的時程壓力。事實上,在2月中這場台北工作坊之後,3月底在舊金山,將舉辦一場初步相容性測試工作坊。該測試將聚焦Tx、Rx與連接等化(Link EQ, LEQ)等電氣測試項目上,因此台北工作坊可以說是一場暖身賽,客戶紛紛利用這個機會做最後衝刺,盡快鎖定需要修正的設計問題,才能趕在三月底的初步相容性測試工作坊前把Bug處理好。安立知的技術團隊也跟客戶的研發工程師們一起,忙得不可開交。

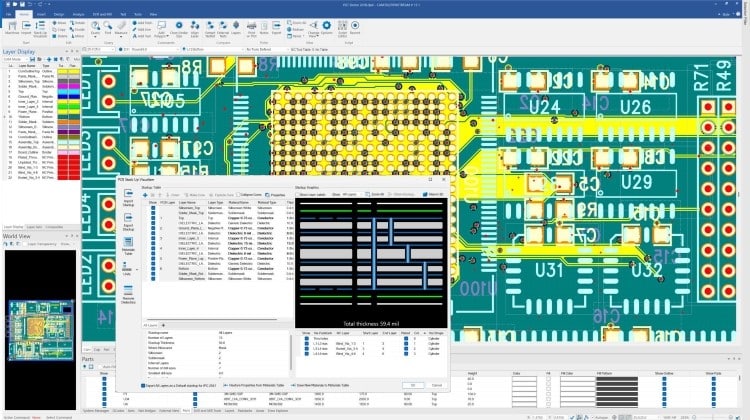

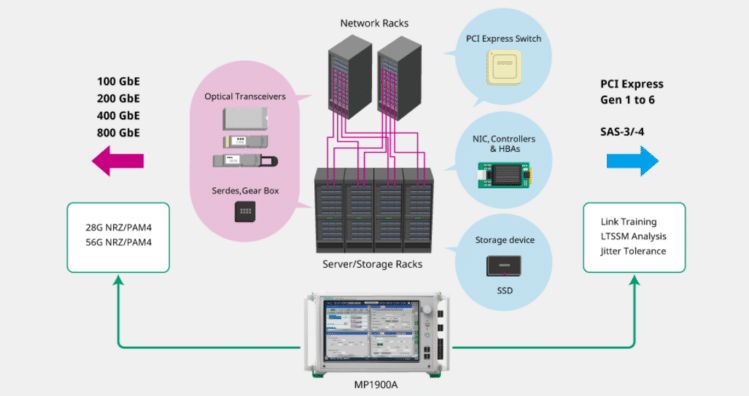

要量測PCIe介面訊號,通常需要由一台即時示波器與一台誤碼率(BERT)分析儀搭建而成的量測系統。安立知的MP1900A系列,就是是一款配有8插槽模組的高性能BERT,可利用PPG/ED、和抖動/雜訊產生器等擴展測量應用,以支援更快速裝置的訊號完整性分析。目前MP1900A可完整涵蓋PCIe 1.0到6.0的測試需求,後續亦可透過升級方案,支援即將展開的PCIe 7.0設計專案。