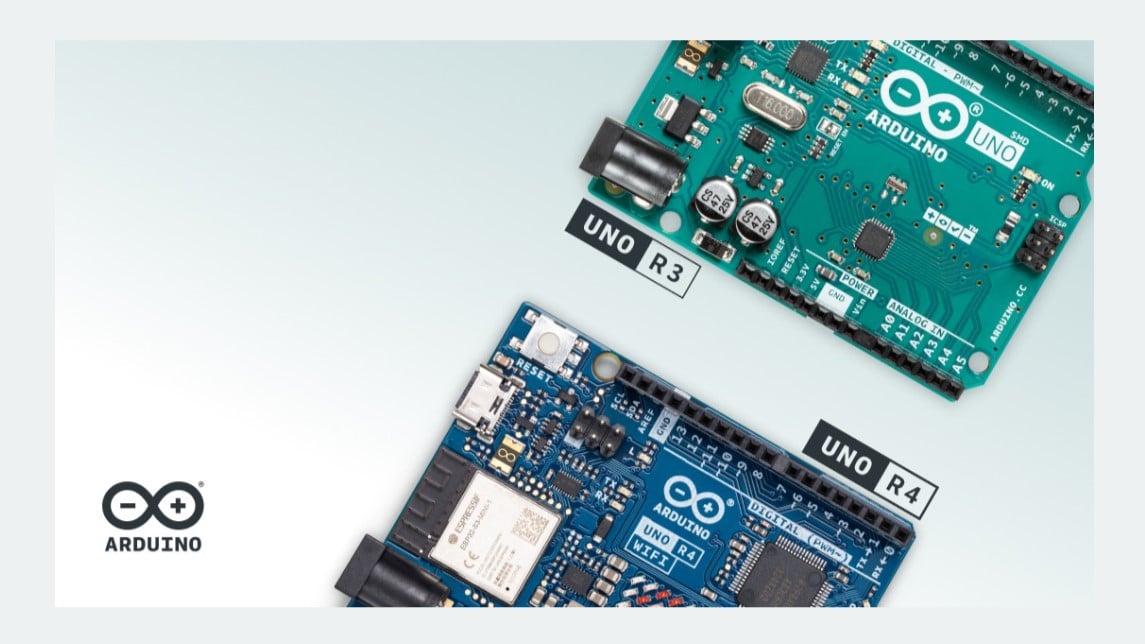

隨著晶片設計、生產製造技術的成熟與提高,第三代半導體功率元件GaN/SiC、微機電系統MEMS器件、矽光子晶片也延用半導體的生產製造技術,延生出了更多領域的應用,並悄悄改變著我們的生活。這些設計領域與傳統電晶片的版圖設計有什麼不一樣?這些差異在Layout驗證上又會有什麼樣的困難與挑戰?本研討會將介紹如何使用Tanner L-Edit快速完成Layout 及使用Calibre驗證 Design Rule Check (DRC)。

●活動名稱:加速第三代半導體功率元件的設計與進階驗證

●主題:

・功率元件(GaN/SiC/MOSFET/IGBT) 的Layout設計挑戰

・Tanner L-Edit針對這些特殊性所提出的解決方案

・如何使用Calibre處理複雜的圖形,完成DRC驗證

●主講人:

Siemens EDA Applications Engineer Consultant / 賴敏誠