賽靈思(Xilinx)宣布推出統一軟體平台「Vitis」,讓軟體工程師與AI科學家在內的廣大開發者都能受惠於靈活應變的硬體優勢。歷經5年時間、總計投入1,000人年打造的Vitis統一軟體平台,讓使用者不需具備硬體專業知識,即可透過軟體或演算法程式碼自行調適與使用賽靈思的硬體架構。

此外,Vitis平台沒有使用特定開發環境的限制,而是透過通用的軟體開發工具與豐富且經最佳化的開源函式庫,讓開發者能專注於演算法的開發。Vitis雖然獨立於支援以硬體程式碼進行編程的Vivado設計套件之外,但它能夠透過將硬體模組封裝為具軟體可調用(Software-callable)的功能,進而提高硬體開發者的工作效率。

賽靈思總裁暨執行長Victor Peng表示,隨著運算需求呈指數型成長,工程師與科學家卻經常受限於晶片固有的效能。賽靈思打造了一個卓越的設計環境,讓所有領域的編程人員與工程師都能使用自己熟悉的工具與框架,共同開發並最佳化軟硬體。這表示使用者能根據自己的應用需求調整其硬體架構,無需換用新的晶片。

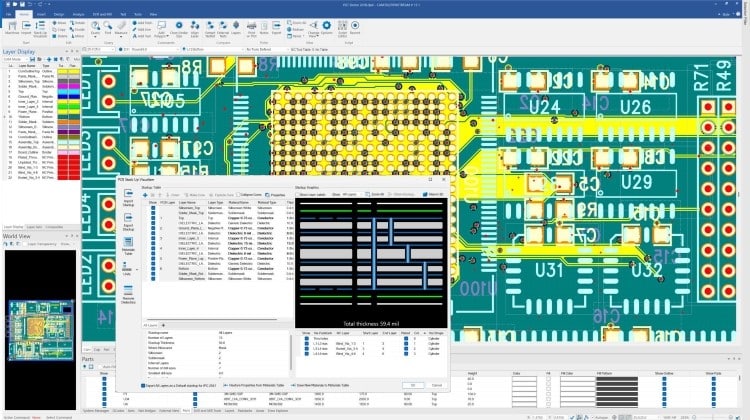

Vitis平台建構在堆疊式架構上,此架構能無縫運用於各種開放原始碼的標準開發系統並組建環境,最重要的是它包含為數眾多的標準函式庫。基礎層為Vitis目標平台,此平台由電路板與預編程I/O組成。第二層為Vitis核心開發套件,包含開源的賽靈思執行時間(runtime)函式庫,用來管理不同領域之間的資料移動。

第三層則是在8個Vitis函式庫中提供超過400個經最佳化的開源應用,包含Vitis基本線性代數子程式函式庫(BLAS)、Vitis Solver函式庫、Vitis安全函式庫、Vitis視覺函式庫、Vitis資料壓縮庫、Vitis計量金融函式庫、Vitis資料函式庫以及Vitis AI資料庫。透過這些函式庫,軟體開發者能使用標準應用程式介面(API)落實硬體加速。Vitis平台的第四層,整合了領域專用架構(DSA)。DSA配置賽靈思硬體,便於開發者使用TensorFlow和Caffe等領先業界的框架進行最佳化與編程。